在開關電源和電機驅動等領域,MOS 管憑借高效的開關速度和低導通電阻成為核心器件。然而,在高頻、大電流的工作環境下,峰值電壓的出現成為影響系統穩定性與設備安全的重要問題。本文深入剖析了 MOS 管峰值電壓產生的原因、對電路的不良影響以及有效的保護措施。

一、MOS 管峰值電壓產生的原因

寄生電容的影響

MOS 管工作時存在內部寄生電容,包括柵源電容(Cgs)和漏源電容(Cds)。在開關過程中,這些寄生電容的充放電行為會導致電壓波動。當 MOS 管從導通轉為截止時,寄生電容電荷迅速釋放,引起漏極瞬時電壓上升。其中,Cgs 在斷電瞬間可能未完全放電,造成柵電壓和漏電壓波動;而 Cds 在關斷時,由于漏源電流迅速減小,其電荷迅速釋放,進一步增加電壓尖峰的發生風險。

電感效應

電路中的導線、器件本身或 MOS 管周圍的元件會產生寄生電感。隨著電流變化率(di/dt)的變化,較大的電感會在關斷 MOS 管時導致電感兩端產生很大的壓降,疊加在漏極電壓上形成峰值電壓。特別地,寄生源極電感(Ls)在關斷時會產生反向峰值電壓,疊加在漏極電壓上,增大峰值電壓幅度。

驅動電路不當

若驅動電路無法對寄生電容快速充放電,會導致柵極電壓不穩定,進而影響漏極電壓。這種情況常見于驅動電流不足或驅動響應速度不夠快的電路中,容易導致斷電時電壓尖峰增大。

負載電流突然變化

當 MOS 管從導通狀態變為截止狀態時,負載電流迅速下降。如果電流變化過快,電感和寄生電容相互作用,可能引起較大的電壓波動,形成峰值電壓。

電源和接地電纜阻抗

在高頻下,電源和接地電纜阻抗可能較高。這些阻抗在 MOS 管快速關斷時會導致電壓波動,產生峰值電壓。在高功率情況下,電源和接地阻抗對峰值電壓的影響尤為顯著。

二、峰值電壓對電路和系統性能的負面影響

器件損壞

過高的峰值電壓會使 MOS 管承受超過額定值的電壓,導致過載、過熱,甚至柵氧化層塌陷。這些問題不僅會縮短 MOS 管的壽命,還可能對其造成直接損壞。

系統性能下降

峰值電壓會引起系統輸出電壓波動,給系統帶來電磁干擾(EMI)和噪聲等問題,降低工作效率和可靠性。對于穩定性要求較高的應用,如精密控制和通信系統,其影響更為嚴重。

復雜的驅動電路設計

為了抑制峰值電壓,設計人員往往需要采取額外措施,如并聯電阻器、電容器或保護二極管等組件,這增加了電路復雜性和成本。

三、降低 MOS 管峰值電壓影響的措施

電路布局優化

良好的 PCB 設計可以有效降低寄生電感和電容對峰值電壓的影響。正確的布線能夠縮短電源與地之間的距離,適當增加去耦電容可以有效降低關鍵路徑寄生電感和峰值電壓幅值,從而進一步抑制電壓波動。

軟開關技術

軟開關技術允許以零或接近零電壓開關頻率進行開關,并引入諧振電容。該技術減少了開關期間的電壓和電流變化,從而減少了峰值電壓的出現,特別適合高頻電路。

加吸收電路

在 MOS 管的漏極和源極之間并聯一個電阻和一個電容,構成吸收電路。這種電路可以有效耗散反向峰值電壓的能量,降低峰值電壓幅值。不過,需要選擇適當的電阻和電容值,以避免對電路其他部分產生負面影響。

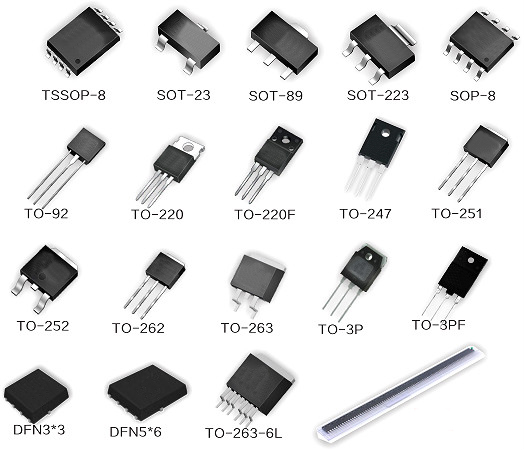

選擇合適的 MOS 管

通過選擇具有較高耐壓的 MOS 管,可以降低電壓尖峰的可能性。同時,還應關注 MOS 管的閾值電壓、最大漏極電流等參數,以確保其在運行環境中的穩定性。

優化 MOS 管驅動電路設計

保證驅動電流充足且響應速度快,在開關 MOS 管時,寄生電容能夠快速充放電,防止柵極電壓波動過大,從而抑制峰值電壓。

綜上所述,MOS 管的峰值電壓問題是高頻電路中常見且嚴重的現象。若處理不當,可能會帶來較大的負面影響。通過采用優化電路布局、軟開關技術、峰值電壓吸收電路等保護措施,并結合實際應用場景分析峰值電壓的原因,可以有效抑制其帶來的問題。隨著電力電子技術的不斷發展,峰值電壓保護技術也在不斷進步。更高效的 MOS 管、更先進的半導體材料和智能驅動設計,為電路峰值電壓抑制提供了更全面的解決方案,有助于保障電子設備的穩定運行和可靠性能。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280